........durch Füllen von Blind Microvias und Through Holes mittels elektrolytischer Kupferabscheidung

Die fortschreitende Miniaturisierung von elektronischen Schaltungen macht zunehmend den Einsatz von HDI-Leiterplatten mit kupfergefüllten Blind Microvias erforderlich. Ein neu entwickelter Kupferelektrolyt, der momentan unter produktionsnahen Bedingungen getestet wird, ermöglicht das defektfreie Füllen von Blind Microvias bei gleichzeitig geringer Kupferschichtdicke auf der Leiterplattenoberfläche. Dies führt zu einem effizienteren Einsatz von Rohstoffen und zu einer kosteneffizienteren Herstellung von Leiterplatten. Ein aktuell in der Entwicklung befindlicher Kupferelektrolyt soll zukünftig auch das zuverlässige Füllen von Durchgangsbohrungen ermöglichen – die gegenwärtigen Entwicklungsarbeiten zeigen bereits erfolgversprechende Resultate.

Increasing the Packaging Density of PCBs by Filling of Blind Micro-vias and Through-holes by Electrodeposition of Copper

The increasing miniaturisation of electronic circuits makes the use of HDI printed circuit boards with copper-filled blind micro-vias, increasingly desirable. A newly-developed copper electrolyte, currently under test in simulated production conditions, will enable defect-free filling of blind micro-vias while at the same time allowing reduced copper deposit thickness on the board surface. This brings with it a more efficient use of materials her and thus a reduction in the cost of PCB manufacture. Another copper electrolyte now under development promises to allow a reliable filling of through-holes. Results obtained to date are extremely promising.

1 Einleitung

In der Mikroelektronik besteht weiterhin der Trend zur Miniaturisierung, das heißt zu kleineren und leistungsfähigeren Systemen, die möglichst auch kostengünstiger als bisherige Systeme sein sollen. Die bekanntesten Beispiele hierfür sind Smartphones und Tablet-PCs, deren Leistungsfähigkeit – trotz gleichbleibender oder sogar kleinerer Gerätegröße – in den letzten Jahren deutlich gesteigert werden konnte. Die große Attraktivität dieser Geräte spiegelt sich in den hohen und ständig wachsenden Verkaufszahlen wider.

Einen wesentlichen Beitrag zur Miniaturisierung leisten HDI-Leiterplatten (engl. HDI: High Density Interconnect), die aufgrund ihrer hohen Integrationsdichte die Signalentflechtung hochfunktioneller elektronischer Bauelemente auf kleinstem Raum ermöglichen. Zur elektrischen Verbindung einzelner Leiterplattenlagen werden hierbei anstatt Durchgangsbohrungen platzsparende Sacklochbohrungen (engl. Blind Microvias) eingesetzt. Durch Füllen der Blind Microvias mit elektrolytisch abgeschiedenem Kupfer (engl. Blind Microvia Filling) lässt sich die Integrationsdichte weiter steigern. Mittlerweile ist der Einsatz von HDI-Leiterplatten nicht mehr allein auf die Mobilelektronik beschränkt, sondern er erfolgt auch zunehmend in anderen Applikationen, zum Beispiel im Automotive-Bereich.

Ein neu entwickelter Elektrolyt, der beim Blind Microvia Filling im Vergleich zur vorangegangenen Elektrolytgeneration nur noch eine sehr geringe Schichtdicke an Kupfer abscheidet, ermöglicht eine ressourcen-, energie- und kosteneffizientere Herstellung von HDI-Leiterplatten. Anhand von Laborergebnissen und Ergebnissen produktionsnaher Tests in einer 7200 L großen vertikalen Durchlaufanlage wird die Leistungsfähigkeit dieses Elektrolyten vorgestellt.

Da sich die Integrationsdichte von HDI-Leiterplatten durch den Einsatz sehr dünner Kernmaterialien noch weiter steigern lässt, wird aktuell die Entwicklung von Elektrolyten zum Füllen von Durchgangsbohrungen (engl. Through Hole Filling) verstärkt. Ergebnisse der Entwicklungsarbeit in diesem Bereich werden präsentiert.

2 Miniaturisierung im Bereich Mikroelektronik

Die bekanntesten Vertreter der fortschreitenden Miniaturisierung in der Mikroelektronik sind die sehr leistungsfähigen Mobilgeräte wie Smartphones und Tablets. Die hohen und ständig wachsenden Verkaufszahlen spiegeln die große Attraktivität dieser Geräte wider. Im Jahr 2013 wurden erstmalig mehr als 1 Milliarde Smartphones verkauft [1], für 2014 wird ein Absatz von circa 1,2 Milliarden und für 2017 von rund 1,8 Milliarden Geräten erwartet [2]. Im Bereich Tablet-PCs wird für 2014 ein Absatz von 271 Millionen Geräten vorhergesagt, dies entspricht gegenüber dem Vorjahr einem Anstieg von nahezu 40 % [3].

Technisch wird die Miniaturisierung in der Mikroelektronik vor allem durch die Entwicklung zunehmend leistungsfähigerer hochfunktionaler Halbleiter-Chips vorangetrieben. Diese werden in Prozessoren mit sehr kleinen Gehäusegrößen und einer sehr großen Anzahl zunehmend rasterförmig angeordneter Anschlüsse verbaut. Abbildung 1 zeigt den Größenvergleich zwischen einem typischen Smartphone-Prozessor und einer 1 Cent-Münze. Die Unterseite des Prozessors weist 976 Anschlüsse auf einer Fläche von knapp 2 cm² auf, dies entspricht rund fünf Anschlüssen pro Quadratmillimeter. Der Abstand (engl. Pitch) der Anschlüsse beträgt hierbei nur 400 µm.

Abb. 1: Größenvergleich zwischen einem Smartphone-Prozessor und einer 1 Cent-Münze

3 Miniaturisierung im Bereich Leiterplatte

Zur platzsparenden und zuverlässigen elektrischen Anbindung von Prozessoren mit außerordentlich hohen Anschlussdichten werden Leiterplatten mit entsprechend hoher Integrationsdichte benötigt. Die klassische Multilayer-Leiterplatte ist hierfür jedoch ungeeignet, da sie zur elektrischen Verbindung einzelner Leiterplattenlagen Durchgangsbohrungen verwendet. Diese weisen relativ große Durchmesser auf und sie erstrecken sich, da sie erst nach dem Verpressen der einzelnen Lagen gebohrt werden, über die gesamte Leiterplattendicke. Dies hat zur Folge, dass auch bei Verbindung direkt benachbarter Lagen der Raum oberhalb und unterhalb der eigentlichen Verbindung verloren geht und somit nicht für andere Strukturen, beispielsweise Leiterbahnen, genutzt werden kann. Die daraus resultierende geringe Integrationsdichte von Multilayer-Leiterplatten ist für die oben beschriebenen Anforderungen nicht ausreichend.

Bereits vor einigen Jahren wurde deshalb eine neue hochintegrierte Leiterplattengeneration, die sogenannte HDI-Leiterplatte, entwickelt, die zunächst überwiegend für die Produktion von Mobiltelefonen eingesetzt wurde. Bei der Herstellung von HDI-Leiterplatten werden die einzelnen Leiterplattenlagen sukzessive aufgebaut (engl. SBU, Sequential Build Up). Bisher wurden diese Aufbaulagen (engl. Build Up Layers) überwiegend auf Multilayer-Kernen aufgebaut – mit steigender Tendenz erfolgt der Aufbau aber auch auf deutlich dünneren Kernen, die in einem späteren Abschnitt dieses Aufsatzes noch näher beschrieben werden. Die elektrische Verbindung jeweils benachbarter Aufbaulagen wird mittels lasergebohrter Blind Microvias realisiert. Abbildung 2 zeigt schematisch den Aufbau einer 2-4-2 HDI-Leiterplatte, das heißt die Leiterplatte besteht aus einem vierlagigen Multilayer-Kern und zwei Aufbaulagen auf jeder Seite.

Abb. 2: Aufbau einer 2-4-2 HDI-Leiterplatte (schematisch)

4 Blind Microvias

Im Vergleich zu Durchgangsbohrungen weisen Blind Microvias kleinere Durchmesser im Bereich von 50 µm bis 150 µm auf und sie erstrecken sich in z-Richtung nur über die Dicke einer Aufbaulage (typischerweise 50 µm bis 150 µm). Sie beanspruchen somit nur so viel Platz, wie tatsächlich für die eigentliche Verbindung erforderlich ist. HDI-Leiterplatten besitzen somit eine wesentlich höhere Integrationsdichte als Multilayer-Leiterplatten und sind deshalb für die Signalentflechtung hochfunktioneller elektronischer Bauelemente auf kleinstem Raum geeignet. Darüber hinaus weisen Blind Microvias aufgrund ihrer deutlich geringeren Größe eine höhere Signalintegrität als Durchgangsbohrungen auf, was sie auch für den Einsatz in Hochfrequenzanwendungen prädestiniert.

Damit Blind Microvias die elektrischen Signale leiten können, werden sie mittels elektrolytischer Kupferabscheidung beschichtet (engl. Blind Microvia Plating). Da bestehende Elektrolyte jedoch keine ausreichende Kupferschichtdicke im unteren Bereich der Blind Microvias abscheiden konnten (Abb. 3a), wurde die Entwicklung spezieller Kupferelektrolyte, die eine ausreichend dicke Kupferschicht abscheiden können (Abb. 3b), erforderlich.

|

|

Abb. 3: Verkupferte Blind Microvias mit einer nicht ausreichenden Dicke im Blind Microvia (a) und einer ausreichenden Dicke der Kupferschicht (b)

4.1 Füllen von Blind Microvias

Eine weitere Steigerung der Integrationsdichte ermöglicht das Übereinanderstapeln von Blind Microvias (engl. Stacked Blind Microvias). Hierfür müssen die Blind Microvias jedoch mit einem elektrisch leitfähigen Material gefüllt werden. Wird zum Füllen anstatt leitfähiger Paste elektrolytisch abgeschiedenes Kupfer verwendet, so führt dies zu folgenden weiteren Vorteilen:

- erhöhte Zuverlässigkeit (die Blind Microvias enthalten nur Kupfer, es ist keine zusätzliche Grenzfläche vorhanden)

- besseres Wärmemanagement (Verlustwärme kann über die sehr gut wärmeleitfähigen, kupfergefüllten Blind Microvias abgeführt werden)

- weitere Steigerung der Integrationsdichte (auf der Leiterplattenoberfläche werden keine zusätzlichen Anschlussflächen (engl. Pads) für die Kontaktierung von Bauelementen benötigt)

Die wesentlichen Prozessschritte bei der Herstellung von HDI-Leiterplatten mit kupfergefüllten Blind Microvias sind in Abbildung 4 schematisch dargestellt. Soll noch eine weitere Lage aufgebaut werden, so ist die Prozessfolge beginnend mit Prozessschritt 2 erneut zu durchlaufen.

Abb. 4: Wesentliche Prozessschritte bei der Herstellung von HDI-Leiterplatten mit kupfergefüllten Blind Microvias

Durch Übereinanderstapeln kupfergefüllter Blind Microvias lassen sich auch nicht-benachbarte Aufbaulagen bei minimalem Platzbedarf elektrisch leitend miteinander verbinden (Abb. 5). All Stacked Blind Microvia Designs ermöglichen den vollständigen Verzicht auf Durchgangsbohrungen. Der Einsatz von Pad-in-Via- beziehungsweise Via-in-Pad Designs führt zu einer weiteren Steigerung der Integrationsdichte, da Bauelementanschlüsse direkt auf die kupfergefüllten Blind Microvias gelötet werden können, sodass hierfür keine zusätzlichen Anschlussflächen notwendig sind (Abb. 6).

Abb. 5: Stacked Blind Microvias

Abb. 6: Via-in-Pad Design (schematisch)

4.2 Bisherige Elektrolyte für Blind Microvia Filling

Typischerweise enthalten Elektrolyte für Blind Microvia Filling eine verhältnismäßig hohe Konzentration an Kupferionen im Bereich von 40 g/l bis 60 g/l in Kombination mit einer niedrigen Schwefelsäurekonzentration im Bereich von 10 ml/l bis 50 ml/l sowie Chloridionen. Die zur Steuerung der Überzugseigenschaften notwendigen organischen Elektrolytzusätze unterscheiden sich von Fachfirma zu Fachfirma, meist sind jedoch folgende drei Komponenten in den Elektrolytzusätzen enthalten:

- Grundzusatz (Inhibitor)

- Kornverfeinerer (Aktivator)

- Einebner (Inhibitor)

Darüber hinaus können sich die Verfahren der unterschiedlichen Anbieter unter anderem auch noch in folgenden Merkmalen unterscheiden:

- Anlagentechnik (standardmäßige Vertikalanlage, vertikale Durchlaufanlage, horizontale Durchlaufanlage)

- Anodentyp (Kupferanode, unlösliche Anode)

- Stromform (Gleichstrom, Pulsstrom, Reverspulsstrom)

- anwendbare Stromdichte

Die bisher von Schlötter angebotenen Verfahren für Blind Microvia Filling arbeiten ausschließlich mit Gleichstrom in standardmäßigen Vertikalanlagen oder vertikalen Durchlaufanlagen. Als Anodenmaterialien sind entweder Kupfer oder Mischmetalloxid (MMO) möglich.

In den Anfangsjahren des Blind Microvia Filling gab es neben den Standardanforderungen an elektrolytisch abgeschiedene Kupferüberzüge für Leiterplatten (z. B. Duktilität, Zuverlässigkeit) im Wesentlichen noch folgende zusätzliche Anforderungen:

- defektfreies Füllen der Blind Microvias ohne Elektrolyteinschlüsse

- Mindestfüllgrad beziehungsweise maximal erlaubte Vertiefung (engl. Dent)

Diese Anforderungen konnten mittels speziell entwickelter Kupferelektrolyte erfüllt werden (Abb. 7).

|

|

Abb. 7: Blind Microvia Filling – schematisch (a) und Schliffbild (b)

Das Schliffbild in Abbildung 7b zeigt ein vorverstärktes Blind Microvia, das vor dem Füllen einen Durchmesser von 138 µm und eine Tiefe von 102 µm aufwies. Während des Füllprozesses wurden im Blind Microvia 93 µm Kupfer (B) abgeschieden, während die Schichtdicke auf der Oberfläche nur 22 µm (C) beträgt, sodass folgende Kennzahlen resultieren:

Vertiefung (A-B): 30,4 µm

Füllgrad (B/A): 75 %

Metallverteilung (B/C): 426 %

Es ist vor allem auf die Wirkungsweise des Einebners zurückzuführen, durch die das Kupfer nicht auf der Oberfläche, sondern bevorzugt in den Blind Microvias, das heißt in den Bereichen niedriger Stromdichte und geringen Elektrolytaustausches, abgeschieden wird. Die Einebnermoleküle adsorbieren während des Füllprozesses vor allem in den Bereichen hoher Stromdichte und starken Elektrolytaustausches. Dadurch wird die Kupferabscheidung in diesen Bereichen erschwert – dies führt zur bevorzugten Abscheidung von Kupfer in den Blind Microvias.

Zur Erzielung eines guten Füllergebnisses müssen die Elektrolytzusätze sehr gut aufeinander abgestimmt sein. Abbildung 8a zeigt ein Blind Microvia vor dem Füllprozess sowie unterschiedliche Ergebnisse, die allein durch Variation der Elektrolytzusätze – bei ansonsten gleichen Abscheideparametern – auftreten können (Abb. 8b–e).

|

|

|

|

Abb. 8: Blind Microvias vor (a) und nach dem Füllprozess bei Variation der Elektrolytzusätze (b–e)

4.3 Neuer Elektrolyt für Blind Microvia Filling

Die Integrationsdichte der Leiterplatten lässt sich durch Verringerung der Leiterbahnbreiten und -abstände noch weiter steigern. Für das Ätzen solcher Feinleiter muss die Kupferschichtdicke auf der Oberfläche jedoch niedrig sein, da es ansonsten zu starker Unterätzung und somit zu Problemen hinsichtlich des Leiterbahnquerschnitts kommen kann.

Wie in Abbildung 4 gezeigt, lässt sich die Kupferschichtdicke nach dem Füllen zwar mittels – eventuell mehrmaligem – Kupferdünnen reduzieren, jedoch sind hierfür zusätzliche Prozessschritte und Anlagen notwendig. Darüber hinaus wird beim Kupferdünnen unmittelbar zuvor abgeschiedenes Kupfer teilweise wieder entfernt, was sich negativ auf die Ressourcen-, Energie- und Kosteneffizienz bei der Leiterplattenherstellung auswirkt. Zur vollständigen Vermeidung – oder zumindest zur Reduzierung – des Kupferdünnens kam deshalb in den letzten Jahren zusätzlich zu den bereits erwähnten Anforderungen noch die Anforderung der Abscheidung einer möglichst geringen Kupferschichtdicke während des Füllprozesses hinzu.

Im Lauf intensiver Entwicklungsarbeit konnte das organische Zusatzsystem so modifiziert werden, dass defektfreies Blind Microvia Filling in Kombination mit sehr geringer Kupferschichtdicke möglich wurde. Der neu entwickelte Elektrolyt Slotocoup SF 30 wurde speziell für den Betrieb mit unlöslichen Anoden entwickelt und ist folgendermaßen zusammengesetzt:

160–240 g/l Kupfersalz BV

15–45 ml/l Schwefelsäure, konz.

50–70 mg/l Chlorid

3–10 ml/l Zusatz Slotocoup SF 31

0,2–1,0 ml/l Zusatz Slotocoup SF 32

0,2–2,0 ml/l Zusatz Slotocoup SF 33

Betrieben wird der Elektrolyt bei Stromdichten von maximal 2 A/dm² im Temperaturbereich zwischen 18 °C und 22 °C.

In Abbildung 9 ist ein Blind Microvia vor und nach einem im Labormaßstab durchgeführten 60-minütigen Füllprozess mit dem genannten Elektrolyten dargestellt. Abbildung 9b zeigt ein vorverstärktes Blind Microvia, das vor dem Füllen einen Durchmesser von etwa 100 µm und eine Tiefe von circa 93 µm aufwies. Während des 60-minütigen Füllprozesses wurden im Blind Microvia 90 µm Kupfer abgeschieden, während auf der Oberfläche nur 4 µm abgeschieden wurden, sodass folgende Kennzahlen resultieren:

Vertiefung: 2,1 µm

Füllgrad: 90 %

Metallverteilung: 2376 %

Im Vergleich zur vorhergehenden Elektrolytgeneration konnte die auf der Oberfläche abgeschiedene Kupferschichtdicke extrem reduziert werden. Dies zeigt sich an der Metallverteilung, die im dargestellten Laborversuch einen extrem hohen Wert von über 2000 % aufweist (Abb. 9b).

|

|

|

Abb. 9: Blind Microvia Filling mit Slotocoup SF 30 im Labormaßstab: vor (a) und nach dem Füllen (b)

Slotocoup SF 30 wird momentan in Kooperation mit dem taiwanesischen Schlötter-Partner AGES im 2012 eröffneten PCB Development Center in Taipeh unter produktionsnahen Bedingungen in einer 7200 Liter großen vertikalen Durchlaufanlage getestet (Abb. 10). Typische Ergebnisse dieser Tests sind in Abbildung 11 bis 13 dargestellt.

Abb. 10: Vertikale Durchlaufanlage mit 7200 Liter Badvolumen im PCB Development Center bei AGES (Taiwan)

Abbildung 11a zeigt ein vorverstärktes Blind Microvia, das vor dem Füllen einen Durchmesser von etwa 108 µm und eine Tiefe von cirka 71 µm aufwies. Während des Füllprozesses wurden im Blind Microvia 74 µm Kupfer abgeschieden, während auf der Oberfläche nur 10 µm abgeschieden wurden. Dies führt zu folgende Kennzahlen:

Vertiefung: 7,0 µm

Füllgrad: 91 %

Metallverteilung: 740 %

In Abbildung 11b ist ein weiteres kupfergefülltes Blind Microvia, das aus der gleichen Leiterplatte wie das Blind Microvia in Abbildung 11a stammt, abgebildet. Bemerkenswert ist, dass trotz nicht-optimaler BMV-Geometrie ein sehr gutes Füllergebnis resultiert.

Abb. 11: Slotocoup SF 30-Testergebnisse des Blind Microvia Filling

Abbildung 11c zeigt ein nicht-vorverstärktes Blind Microvia, das vor dem Füllen einen Durchmesser von cirka 98 µm und eine Tiefe von etwa 68 µm aufwies. Während des Füllprozesses wurden im Blind Microvia 76 µm Kupfer abgeschieden, während auf der Oberfläche nur 10 µm abgeschieden wurden, sodass folgende Kennzahlen resultieren:

Vertiefung: 5 µm

Füllgrad: 96 %

Metallverteilung: 760 %

Slotocup SF 30 ermöglicht auch das defektfreie Füllen eng beieinanderliegender Blind Microvias bei gleichzeitig geringer Schichtdicke der Kupferoberflächen. Abbildung 12 zeigt das Füllergebnis bei einem Blind Microvia Pitch von lediglich 200 µm.

|

|

Abb. 12: Slotocoup SF 30-Testergebnisse beim Füllen eng beieinanderliegender Blind Microvias

Abb. 13: Slotocoup SF 30-Testergebnisse beim Füllen sehr flacher Blind Microvias

Sehr flache Blind Microvias, die beim Einsatz extrem dünner Dielektrika resultieren, lassen sich mit dem neuen Elektrolyten ebenfalls defektfrei füllen, jedoch resultieren hierbei etwas höhere Kupferschichtdicken (Abb. 13).

Die Tests unter produktionsnahen Bedingungen bestätigen, dass Slotocoup SF 30 sehr gutes Blind Microvia Filling in Kombination mit extrem geringer Dicke der Kupferschicht ermöglicht. Nach erfolgreichen Bemusterungen für mehrere asiatische Leiterplattenhersteller ist für das zweite Quartal 2014 die erste Installation bei einem Kunden geplant.

5 Through Hole Filling

Eine weitere Steigerung der Integrationsdichte von HDI-Leiterplatten lässt sich durch den Ersatz der bisher üblicherweise verwendeten, relativ dicken Multilayer-Kerne durch deutlich dünnere Kerne mit Dicken zwischen 100 µm und 200 µm erzielen. Da die Dicke eines derartigen Innenlagenkerns der Dicke der Aufbaulagen sehr ähnlich ist, wird in diesem Zusammenhang auch von einem kernlosen Aufbau gesprochen. Der in Abbildung 14 gezeigte All Stacked Blind Microvia Aufbau enthält einen 100 µm dicken Kern, der kupfergefüllte Blind Microvias aufweist.

Abb. 14: Kernloser Aufbau

Sehr dünne Kerne können anstatt Blind Microvias auch Durchgangsbohrungen aufweisen. Bisher wurden diese Durchgangsbohrungen nach dem ersten Verkupfern zunächst mit Paste verfüllt und anschließend, zur Erzeugung der Pads, erneut verkupfert. Die Herstellung derartiger Kerne ist somit sehr aufwändig und teuer. Außerdem kann der Einsatz der Paste zu Zuverlässigkeitsproblemen führen.

In Analogie zum Blind Microvia Filling lässt sich durch das Füllen der Durchgangsbohrungen mit elektrolytisch abgeschiedenem Kupfer die Zuverlässigkeit steigern und das Wärmemanagement verbessern. Der Aufbau von jeweils zwei Aufbaulagen auf jeder Seite eines dünnen Kerns mit kupfergefüllten Durchgangsbohrungen ist in Abbildung 15 schematisch dargestellt.

Abb. 15: Kernloser Aufbau (schematisch)

5.1 Neue Elektrolyte für Through Hole Filling

Zunächst wurde versucht, die bereits beim Blind Microvia Filling bewährten Kupferelektrolyte auch im Bereich Through Hole Filling einzusetzen. Es zeigte sich jedoch, dass diese Elektrolyte nicht für diese Applikation geeignet sind, sodass weitere Entwicklungsarbeit notwendig wurde. Einige Laborergebnisse der aktuellen Entwicklungsarbeit sind in Abbildung 16 gezeigt.

Abb. 16: Through Hole Filling nach Modifizierung der Elektrolytzusammensetzung

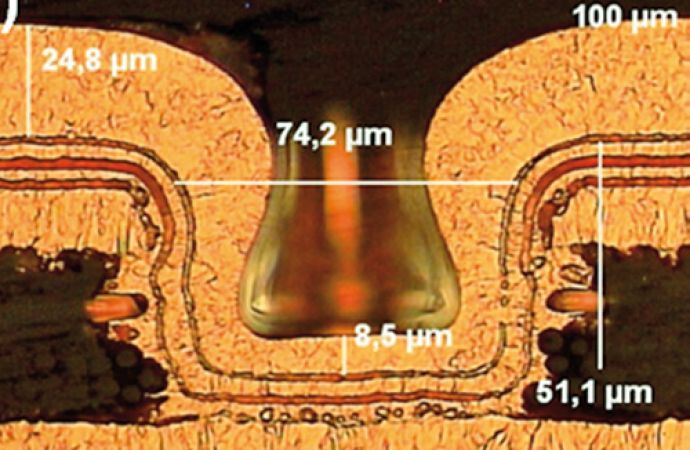

Durch Modifizierung der Elektrolytzusammensetzung gelang es, das Füllen von Durchgangsbohrungen (circa 85 µm Bohrlochdurchmesser/circa 110 µm Bohrlochtiefe) deutlich zu verbessern. Alle vier in Abbildung 16 gezeigten Abscheidungen wurden jeweils mit Gleichstrom bei gleicher Abscheidedauer und Stromdichte durchgeführt. Darüber hinaus wurde während der gesamten Abscheidedauer jeweils nur in einem Elektrolyten abgeschieden, das heißt es erfolgte kein Elektrolytwechsel im Laufe der Abscheidung.

Mit steigendem Aspektverhältnis, das heißt abnehmendem Bohrlochdurchmesser und/oder zunehmender Bohrlochtiefe, wird der Stofftransport und somit auch die Nachlieferung von Kupferionen erschwert. Dies hat zur Folge, dass eine defektfreie Füllung der Durchgangsbohrungen ohne Elektrolyteinschlüsse zunehmend schwieriger wird. Abbildung 17 zeigt zwei Füllergebnisse von nicht-vorverstärkten Durchgangsbohrungen (circa 50 µm Bohrlochdurchmesser/ circa 160 µm Bohrlochtiefe).

Der im Defekt (Abb. 17a) eingeschlossene Elektrolyt dehnt sich beim Erwärmen der HDI-Leiterplatte aus und kann somit bereits während des Auflötens von Bauelementen oder bei einer späteren Temperaturbelastung zu einem Riss in dieser Verbindung führen, was einen Systemausfall zur Folge haben kann. Im Fokus der aktuellen Entwicklungsarbeit steht deshalb das zuverlässig defektfreie Füllen von Durchgangsbohrungen mit unterschiedlichen Aspektverhältnissen (Abb. 17b).

Abb. 17: Through Hole Filling: mit (a) und ohne Elektrolyteinschluss (b)

6 Zusammenfassung

Moderne Mikroprozessoren tragen wegen ihrer hohen Funktionalität und ihrer geringen Größe einen wesentlichen Anteil zur fortschreitenden Miniaturisierung im Bereich der Mikroelektronik bei. Aufgrund ihrer hohen Integrationsdichte ermöglichen HDI-Leiterplatten die zuverlässige Entflechtung der hohen Anschlussdichten dieser Mikroprozessoren auf kleinstem Raum.

Durch das Füllen von Blind Microvias mit elektrolytisch abgeschiedenem Kupfer lässt sich die Integrationsdichte von HDI-Leiterplatten weiter steigern. Der neu entwickelte Elektrolyt Slotocoup SF 30, der aktuell in Taiwan unter produktionsnahen Bedingungen getestet wird, ermöglicht defektfreies Füllen bei gleichzeitig niedriger Kupferschichtdicke. Dies führt zu einer weiteren Steigerung der Integrationsdichte und zu einer ressourcen-, energie- und kosteneffizienteren Herstellung von HDI-Leiterplatten. Die erste Installation bei einem Kunden soll im zweiten Quartal 2014 erfolgen.

Mittels sogenannter kernloser Aufbauten, die aus sehr dünnen Kernmaterialien bestehen, kann die Integrationsdichte noch weiter gesteigert werden. Ergebnisse der aktuellen Entwicklungstätigkeit zeigen, dass mittels Gleichstromabscheidung von Kupfer das Füllen der in diesen Kernen vorhandenen Durchgangsbohrungen prinzipiell möglich ist. Da das Füllergebnis und somit die Qualität der Verbindung vom Aspektverhältnis der Durchgangsbohrungen abhängt, steht momentan die Realisierung eines zuverlässig defektfreien Füllens bei unterschiedlichen Aspektverhältnissen im Vordergrund der Entwicklungsarbeit.

Danksagung

Der Autor bedankt sich bei der AGES Group (Taiwan) und speziell bei Mr. Albert Yeh für die Unterstützung in diesem Projekt.

Literatur

[1] International Data Corporation (IDC): Worldwide Quarterly Mobile Phone Tracker; Januar 2014

[2] NPD DisplaySearch: Smartphone Quarterly report; November 2013

[3] Gartner: Forecast: PCs, Ultramobiles, and

Mobile Phones, Worldwide, 2011-2018, 1Q14 Update, März 2014

DOI:10.7395/2014/Dietterle1